AMD, по всей видимости, готовится к серьезному изменению в архитектуре своих будущих процессоров «Zen 6», отходя от традиционных межчиповых соединений на основе последовательных каналов SERDES (Serializer/Deserializer).

Новая технология, называемая «Sea-of-Wires» (Море проводов), предполагает использование широкого параллельного соединения, прокладываемого через многослойный корпус RDL (Redistribution Layer).

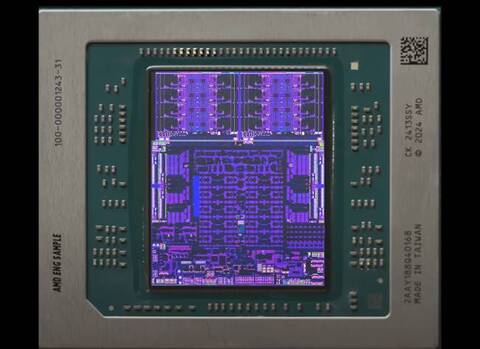

Первые намеки на это изменение были замечены на фотографиях APU Strix Halo. Образцы демонстрируют прямоугольное поле контактных площадок там, где раньше располагался крупный блок SERDES. Эти блоки, занимавшиеся сериализацией и десериализацией данных, были необходимы для передачи информации между отдельными кристаллами (CCD) по высокоскоростным последовательным каналам. Данная операция потребляет энергию и добавляет задержку из-за накладных расходов кодирования, декодирования и восстановления тактовой частоты.

Преимущества параллельного подхода:

Переход на множество коротких параллельных проводников позволяет AMD устранить повторяющуюся работу блоков PHY (Physical Layer) и значительно снизить задержки при обмене данными между кристаллами. Такой подход не только минимизирует задержку, но и позволяет легко масштабировать пропускную способность путем простого добавления физических линий.

Кроме того, это освобождает пространство, которое ранее занимали блоки SERDES, позволяя размещать компоненты, такие как CCD, контроллеры памяти и специализированные ускорители, ближе друг к другу. Это, в свою очередь, ведет к уменьшению затрат на коммуникацию.

Инженерные вызовы:

Однако у новой технологии есть и свои компромиссы. Упаковка большого количества параллельных дорожек под кристаллом повышает требования к целостности сигнала, эффективному теплоотводу, маршрутизации и сложности производства. Успех этого проекта будет зависеть от тесного сотрудничества команд, разрабатывающих как сами кристаллы, так и корпус (упаковку), особенно при работе с многослойным RDL.

1’>

Если AMD сможет успешно интегрировать подход Sea-of-Wires в свою архитектуру Zen 6, это может привести к значительному улучшению эффективности (производительность на ватт) и уменьшению задержки для рабочих нагрузок. В частности, ожидается более быстрая работа с памятью благодаря сниженной задержке кристалла ввода/вывода.

Павлик Александр

Источник: ru.gecid.com