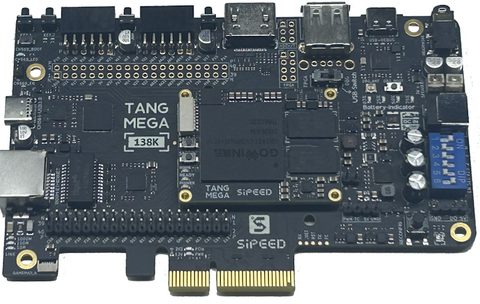

Разработчик опубликовал проект 486Tang — процессора 486SX-20 на плате ПЛИС, размер которой не больше кредитной карты.

486Tang — проект порта ядра ao486 MiSTer PC на ПЛИС Sipeed Tang Console 138K. По словам автора, это первая попытка портировать ao486 на FPGA, не относящийся к Altera.

Он подробно описывает, как пришлось адаптировать ядро и архитектуру под ограничения платы Tang. В случае с памятью (RAM) на MiSTer используется DDR3, тогда как на Tang — SDRAM как основная память. Tang-плата SDRAM 16-битная, тогда как ao486 нужен 32-битный доступ. Чтобы обойти это ограничение, автор провёл «double-pumping» (логика SDRAM работает вдвое быстрее системного такта), чтобы можно было считывать/записывать 32-битные значения за один такт CPU.

Кроме того, на MiSTer IDE-запросы обрабатываются через ARM HPS, который читает образы дисков. Tang не имеет такого быстрого интерфейса между MCU/ARM-подсистемой и FPGA. Разработчик решил использовать SD-карту для хранения образов и BIOS/IDE данных, а FPGA напрямую обращается к ней.

Также он создал загрузчик (boot loader), который загружает BIOS, VGA BIOS, ID-данные IDE, и CMOS настройки из первых 128 KB SD-карты перед тем, как дать контроль CPU.

Плата Tang имеет менее мощный FPGA (Gowin GW5A), поэтому производительность изначально была невысокой.

В рамках оптимизации пришлось сократить длинные логические пути (critical paths) путём вставки регистров (pipeline) или репликации цепей, особенно reset-сигналов, а также уменьшения fan-out (числа элементов, подключённых к одной точке).

Также потребовалась оптимизация инструкции выборки (instruction fetch), чтобы снизить критические задержки при декодировании и обработке инструкций с переменной длиной.

Наконец, автор изменил структуру TLB (Translation Lookaside Buffer): из полностью ассоциативного сделал его 4-сторонним (4-way set associative).

В итоге, судя по тестам, прирост производительности составил около 35%, а система достигла уровня производительности 486SX-20.

Автор подчёркивает, что подгонка под такую небольшую FPGA — это всегда компромиссы, так как нужно учитывать тактовую частоту, размер буферов, задержку и ограниченность ресурсов. Он сделал вывод, что прирост тактовой частоты — самый эффективный способ улучшения производительности на данном этапе, который даёт больше, чем добавление кэшей или усложнение конвейера.

Источник: habr.com