Обучение современных генеративных ИИ-моделей требует колоссальных вычислительных ресурсов. Используются кластеры из сотен тысяч ускорителей (XPU), и их число растет. Для обеспечения необходимой производительности при одновременном снижении энергопотребления и стоимости требуется всё более изощрённая интеграция вычислительных блоков, памяти и интерфейсов ввода-вывода. Традиционные подходы, такие как закон Мура и масштабирование техпроцессов, в данной области уже не поспевают за прогрессом. В связи с этим передовая интеграция System-in-Package (SiP) становится ключом к созданию XPU следующего поколения.

Компания Broadcom разработала инновационную платформу 3.5D eXtreme Dimension System in Package (XDSiP). Она нацелена на создание специализированных вычислительных платформ для задач искусственного интеллекта и высокопроизводительных вычислений, обещая значительный прирост в производительности и энергоэффективности.

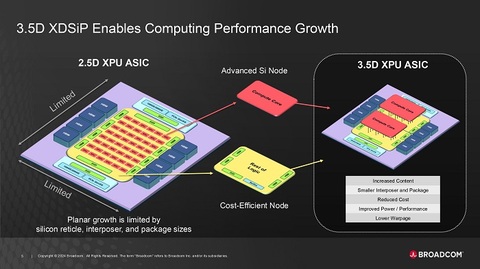

За последнее десятилетие 2.5D-интеграция, предполагающая размещение на общей подложке нескольких чиплетов и модулей HBM, доказала свою эффективность при разработке XPU. Однако обучение новых, ещё более сложных больших языковых моделей, диктует необходимость перехода к 3D-компоновке кремния для оптимизации габаритов, энергопотребления и стоимости. Таким образом, именно 3.5D-интеграция, сочетающая 3D-компоновку с 2.5D-корпусировкой, обещает стать доминирующей технологией для XPU следующего поколения в ближайшее десятилетие.

Новая платформа 3.5D XDSiP от Broadcom ориентирована на создание крупномасштабных ИИ-ускорителей нового поколения. Она позволяет разместить в одном корпусе свыше 6000 мм² кремния и до 12 стеков памяти HBM, что обеспечивает высокую эффективность и низкое энергопотребление, необходимые для масштабных ИИ-вычислений. Кроме того, Broadcom первой в отрасли разработала 3.5D XPU с компоновкой Face-to-Face (F2F).

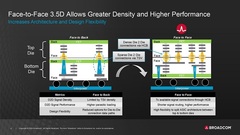

Отличительной особенностью 3.5D XDSiP является значительное повышение плотности межсоединений и энергоэффективности по сравнению с традиционным подходом Face-to-Back (F2B). Принципиально новая компоновка F2F предполагает прямое соединение верхних металлических слоев верхнего и нижнего кристаллов, что гарантирует плотное и надежное соединение с минимальными электрическими помехами и высочайшей механической прочностью. Платформа включает в себя набор IP-блоков и проприетарный процесс проектирования, обеспечивающий корректную 3D-компоновку кристаллов по таким параметрам, как питание, синхронизация и сигнальные соединения.

Ключевые преимущества 3.5D XDSiP от Broadcom:

Семикратное увеличение плотности межсоединений: значительно превосходит показатели технологии F2B. Десятикратное снижение энергопотребления: в интерфейсах die-to-die благодаря использованию 3D HCB вместо планарных PHY. Минимизация задержек: оптимизировано время передачи данных между вычислительными компонентами, памятью и интерфейсами ввода-вывода в 3D-стеке. Компактный форм-фактор: уменьшенные размеры подложки и корпуса ведут к снижению себестоимости и улучшению плоскостности.Первый 3.5D XPU от Broadcom, выполненный по технологии F2F, объединяет четыре вычислительных кристалла, один кристалл ввода-вывода и шесть модулей HBM. В нем применены передовые техпроцессы TSMC и технология 2.5D-корпусировки CoWoS. Несмотря на исключительную сложность чипа, проприетарный процесс проектирования и методология автоматизации Broadcom, базирующиеся на стандартных инструментах, обеспечили успех с первой же попытки.

Уже сейчас более пяти продуктов находятся в разработке с использованием технологии 3.5D, а большинство клиентов Broadcom в сфере потребительского ИИ перешли на платформу 3.5D XDSiP. Старт серийных поставок запланирован на февраль 2026 года. Новый 3.5D XDSiP продемонстрировал полную работоспособность и превосходную производительность критически важных IP-блоков, включая высокоскоростные SerDes, интерфейсы памяти HBM и межсоединения die-to-die. Это в очередной раз подтверждает высочайший уровень экспертизы Broadcom в области проектирования и тестирования сложных 3.5D-интегральных схем.

Источник: overclockers.ru