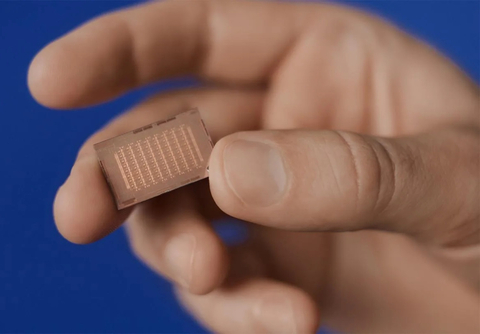

Компания Meta✴ поделилась подробностями о следующем собственных ИИ-ускорителей Meta✴ Training and Inference Accelerator. Новый чип отличается более высокой производительностью по сравнению со чипом MTIA v1, представленным в мае прошлого года, и будет играть решающую роль в обеспечении работы ИИ-моделей Meta✴.

Следующее поколение крупномасштабной инфраструктуры Meta✴ рассчитано на поддержку новых продуктов и услуг в области генеративного ИИ, рекомендательных систем и передовых исследований в области ИИ. Создание нового чипа является частью инвестиций в инфраструктуру. В ближайшие годы, как ожидается, затраты в этом направлении будут расти, поскольку требования к вычислительным ресурсам для поддержки моделей будут расти вместе с усложнением последних.

Источник изображений: Meta✴

Архитектура чипа ориентирована на обеспечение «правильного баланса вычислений, пропускной способности и объёма памяти» даже при относительно небольших размерах обрабатываемых последовательностей. MTIA v2 в сравнении с MTIA v1 в 3,5 раза быстрее в обычных вычислениях и в 7 раз — в разреженных. Новый чип изготавливается по 5-нм техпроцессу TSMC и имеет габариты 25,6 × 16,4 мм (упаковка 40 × 50 мм). Ускоритель работает на частоте 1,35 ГГц, а его TDP составляет 90 Вт, тогда как 7-нм MTIA v1 работал на частоте 800 МГц и имел TDP всего 25 Вт. Готовая стоечная система вмещает до 72 ускорителей и состоит из трёх шасси с 12 платами, на каждой из которых размещено по два ускорителя. Для дальнейшего масштабирования можно добавить RDMA-сеть.

Чип состоит из 64 вычислительных элементов (PE). У каждого PE есть небольшой блок локальной памяти объёмом 384 Кбайт с ПСП 1 Тбайт/с. На весь чип приходится 256 Мбайт SRAM (2,7 Тбайт/с), а внешняя память представлена 128 Гбайт LPDDR5 (204,8 Гбайт/с). Для подключения к хосту используется интерфейс PCIe 5.0 x8 (32 Гбайт/с). При работе с матрицами чип развивает 177 (FP16/BF16) и 354 (INT8) Тфлопс, в разреженных вычислениях — вдвое больше. SIMD-блоки выдают 2,76 Тфлопс для FP32 и 5,53 Тфлопс для INT8/FP16/BF16. В векторных расчётах значения те же, только для INT8 показатель составляет уже 11,06 Тфлопс.

MTIA v2 совместим с кодами, разработанными для MTIA v1. Стек MTIA ориентирован на PyTorch 2.0 и включает компилятор Triton-MTIA. Предварительные испытания MTIA v2 на четырёх ключевых ИИ-моделях компании показали, что он втрое быстрее MTIA v1 чип первого поколения. А на уровне платформы достигнуто шестикратное увеличение пропускной способности модели и рост производительности на Вт в 1,5 раза. Чипы MTIA уже развёрнуты в ЦОД компании. Правда, для обучения Meta✴ их пока не использует.

Источник: servernews.ru